高效人工智能系统的软硬件协同设计 陈怡然教授在杜克大学的探索与人工智能基础软件开发

在人工智能浪潮席卷全球的今天,计算效率已成为制约AI模型规模扩展与实时应用的关键瓶颈。传统上,硬件设计与软件开发往往各行其道,导致专用芯片难以充分发挥潜力,或通用软件无法充分利用硬件特性。杜克大学电子与计算机工程系教授陈怡然及其团队,正致力于打破这一壁垒,通过软硬件协同设计(Hardware-Software Co-design)方法论,构建下一代高效人工智能系统,并推动其基础软件开发范式的革新。

一、软硬件协同设计的核心理念

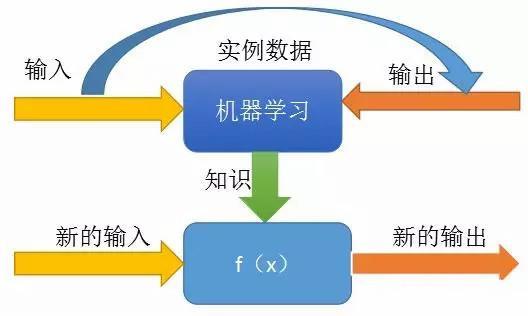

陈怡然教授的研究核心在于认识到,人工智能,尤其是深度学习,对计算、存储和通信的需求具有独特的模式。传统的通用计算架构(如CPU)在处理大规模矩阵运算、高维张量和稀疏数据时效率低下。因此,必须从算法、编译器、系统软件到硬件架构进行一体化设计与优化。

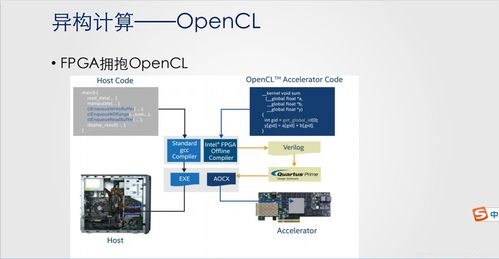

协同设计的精髓是“相互适应”:一方面,硬件(如专用集成电路ASIC、现场可编程门阵列FPGA、存内计算芯片)需要为AI计算的核心操作(如卷积、注意力机制)进行定制化设计,提供极高的能效比和吞吐量;另一方面,软件栈(包括编程模型、编译器、运行时库、框架)需要“感知”底层硬件的独特能力,将高级AI模型高效地映射到物理计算单元上,并管理数据流动与内存层次。

二、关键研究方向与创新

- 面向新型硬件的神经网络架构搜索(NAS)与模型压缩:陈怡然团队探索如何让神经网络模型的设计过程,自动将目标硬件的约束(如功耗、面积、内存带宽)作为优化目标。这避免了“先设计模型,后艰难适配硬件”的被动局面,直接从源头产生“硬件友好型”的高效模型。

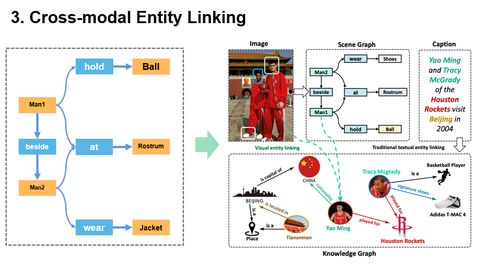

- 智能编译与调度技术:开发能够理解AI计算图与异构硬件(可能包含CPU、GPU、AI加速器等多种处理单元)的先进编译器。它能自动进行算子融合、内存优化、流水线调度,并将计算任务动态分配到最合适的硬件单元上,实现系统级能效最大化。

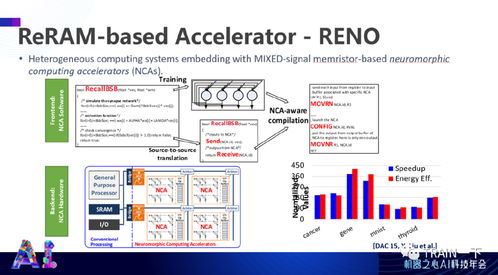

- 存算一体与近存计算:这是陈怡然教授的重点领域之一。通过打破“内存墙”(数据在处理器与内存之间频繁搬运带来的巨大能耗与延迟),直接在存储器内部或附近完成计算。这需要软硬件深度协同:硬件上设计新的存储单元和电路;软件上则需要全新的数据布局、编程抽象和算法来利用这种非冯·诺依曼架构。

- 可靠性与安全性协同设计:在追求极致效率的必须确保AI系统的可靠与安全。团队研究如何从硬件层面(如针对近似计算、软错误的容错设计)和软件层面(如对抗性攻击的检测与防御)协同构建鲁棒的AI系统。

三、对人工智能基础软件开发的影响

陈怡然教授的研究深刻影响着AI基础软件的开发方向:

- 从“硬件无关”到“硬件感知”:未来的AI框架(如TensorFlow、PyTorch的演进版本)可能需要内嵌硬件特性数据库和成本模型,使开发者能在编写代码时预估不同硬件平台上的性能与能效。

- 抽象层次的重新定义:为了兼容多样化的定制硬件,可能需要更高层次或更领域特定(Domain-Specific)的编程抽象和中间表示(IR),让编译器承担更多底层优化的责任。

- 系统软件栈的垂直整合:操作系统、驱动程序和运行时环境需要更紧密地与AI加速器耦合,实现细粒度的资源管理和能耗控制,支持动态的、混合精度的工作负载。

- 开源生态与标准化:推动软硬件接口、基准测试套件和优化工具链的开源,是促进整个协同设计生态繁荣的关键。杜克大学的相关研究往往以开源形式发布,助力社区共同进步。

四、未来展望

随着人工智能模型向万亿参数迈进,应用场景向边缘和终端设备渗透,对效率的需求将愈发严苛。陈怡然教授在杜克大学引领的软硬件协同设计研究,正为这个挑战提供根本性的解决方案。这不仅意味着更强大、更节能的AI芯片,更意味着一个全新的、从算法到硅片的协同创新生态。人工智能基础软件开发将不再仅仅是编写模型代码,而是需要与硬件特性深度对话,共同谱写高效智能计算的新篇章。这条路线的成功,将决定AI技术能否真正大规模、可持续地赋能千行百业,融入我们生活的每一个角落。

如若转载,请注明出处:http://www.bxtsu.com/product/12.html

更新时间:2026-04-15 21:20:00